김기남 삼성전자 부회장 [사진=삼성전자 제공]

김기남 삼성전자 DS부문장(부회장)은 대만 TSMC가 지난해 사상 최대 실적을 달성하는 등 글로벌 파운드리(반도체 위탁생산) 시장에서 삼성과 격차를 벌리고 있다는 세간의 우려에 대해 지난 20일 기자와 만나 이같이 밝혔다.

삼성전자가 '2030년 비메모리 1위'를 목표로 3나노미터(㎚) 등 최첨단 미세공정 개발에 집중하고 있는 만큼 경쟁자를 의식하지 않겠다는 자신감으로 풀이된다.

삼성전자와 TSMC는 초미세 공정 선두 자리를 두고 치열한 경쟁을 벌이고 있다. 전 세계 파운드리 업체 가운데 7나노 이하 파운드리 미세공정은 삼성전자와 TSMC만이 가능하다.

TSMC도 이에 맞불을 놓는다. TSMC는 오는 4월 29일 북미 기술 심포지엄에서 3나노 공정기술을 공개한다는 방침이다. 또 올해 160억 달러(약 19조원)를 투자해 양산에 속도를 낸다. 회사는 투자금액 중 80%를 7나노, 5나노, 3나노 등의 생산능력 확대에 사용하겠다고 밝혔다. 대만 타이난 사이언스 파크에 3나노 공정을 적용할 새 파운드리 공장 건설에도 돌입한 것으로 알려졌다.

양사가 모두 3나노 개발에 성공한 만큼 경쟁의 핵심은 '양산 시점'이 될 것으로 보인다. 김 부회장은 3나노 양산 시점에 대해 "영업비밀도 있고, 고객사와 관련된 부분도 있어 밝힐 수 없다"면서도 "우리 나름의 플랜대로"라고 말했다.

3나노는 반도체 회로 선폭을 의미한다. 선폭이 좁을수록 소비전력이 감소하고 처리 속도가 향상된다. 3나노 공정기술로 개발한 칩은 5나노에 비해 칩 면적을 약 35% 이상 줄일 수 있고, 소비전력은 50% 감소시키면서 성능(처리속도)은 약 30% 향상시킬 수 있다. 3나노 공정을 먼저 양산하게 되면 반도체 설계업체로부터 최신 반도체 물량을 수주할 가능성이 커진다.

김 부회장은 삼성전자가 파운드리 사업을 확대하기 위해 사업부를 별도 자회사로 분리할 가능성에 대해서는 "그런 건 없다"고 선을 그었다. 삼성전자는 현재 시스템 반도체를 직접 만드는 시스템LSI와 설계를 받아 생산만 담당하는 파운드리 사업부, 메모리 반도체를 만드는 메모리 사업부 모두를 보유하고 있다.

김 부회장은 올해 겸직하고 있던 종합기술원장직을 황성우 신임 사장에게 물려주고, DS부문장 역할에만 집중한다. 그는 "파운드리, 시스템LSI, 메모리 모두 다 열심히 해야 한다"고 강조했다.

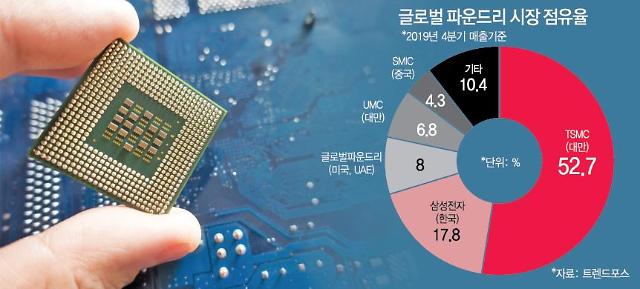

한편, 시장 조사업체 트렌드포스에 따르면 지난해 4분기 기준 글로벌 파운드리 시장에서 TSMC는 52.7%의 시장 점유율을 기록했다. 반면 삼성전자는 17.8%에 그쳤다.

©'5개국어 글로벌 경제신문' 아주경제. 무단전재·재배포 금지

![[르포] 중력 6배에 짓눌려 기절 직전…전투기 조종사 비행환경 적응훈련(영상)](https://image.ajunews.com/content/image/2024/02/29/20240229181518601151_258_161.jpg)