SK하이닉스는 3세대 10나노급(1z) 미세공정을 적용한 16기가비트(Gbit) DDR4 D램을 개발했다고 21일 밝혔다.

D램은 PC나 정보기술(IT) 기기에서 정보를 기록·전달하고 이를 읽거나 수정·처리할 수 있는 메모리다. DDR 램은 1→2→3→4로 세대가 바뀜에 따라 동작 속도와 전력소비 등 D램의 성능도 개선되고 있다.

속도와 용량이 늘어날수록 전기 신호를 전달하는 회로의 폭은 더 좁아져야 한다. 10나노는 전기 신호를 전달하는 회로의 폭을 1억분의1m인 10㎚대로 그려낼 수 있는 공정이다. 공정은 단계별로 1x, 1y, 1z로 구분하는데, x에서 z로 갈수록 더 미세해진다. 칩이 작아지면 웨이퍼 1장에 들어가는 칩의 개수가 늘어나면서 생산성도 높아지게 된다.

생산성은 2세대(1y) 제품 대비 약 27% 향상되며 원가 경쟁력도 높아졌다. 초고가의 극자외선(EUV) 노광 공정 없이도 생산이 가능하다.

데이터 전송 속도는 DDR4 규격의 최고 속도인 3200Mbps까지 지원한다. 2세대 8Gb 제품으로 만든 동일 용량의 모듈보다 전력 소비를 약 40% 줄여 전력 효율도 개선했다. 특히 3세대 제품은 이전 세대 생산 공정에는 사용하지 않던 신규 물질을 적용해 D램 동작의 핵심 요소인 정전용량을 극대화했다.

SK하이닉스는 차세대 모바일 D램인 LPDDR5와 초고속 D램 고대역폭메모리(HBM)3 등 다양한 응용처에 사용될 3세대 10나노급 미세공정 기술을 확대 적용해나갈 계획이다.

이정훈 SK하이닉스 D램 개발사업 1z 태스크포스(TF)장은 "이번 D램은 고성능·고용량 D램을 찾는 고객들의 수요 변화에 적합한 제품"이라며 "내년부터 본격 공급에 나서 시장 수요에 적극 대응할 것"이라고 말했다.

SK하이닉스의 3세대 DDR4 D램 개발은 삼성전자와 마이크론에 이어 세 번째다. 삼성전자는 올해 3월 3세대 10나노급(1z) 8Gbit 제품을 개발 완료한 데 이어 지난 9월부터 양산에 돌입했다. 마이크론은 8월부터 10나노급(1z) 16Gbit 제품을 양산 중이다. SK하이닉스 역시 올해 안에 양산 준비를 완료하고 내년부터 본격적으로 양산에 돌입할 예정이다.

반도체업계 관계자는 "올해 반도체 경기가 좋지 않지만 삼성전자와 SK하이닉스 등 반도체 업체들이 내년으로 예상되는 업황 회복기에 대비하고 있다"며 "특히 향후 미세공정 수요가 더 커질 것으로 예상되면서 업체들의 제품 개발이 활발해질 것"으로 내다봤다.

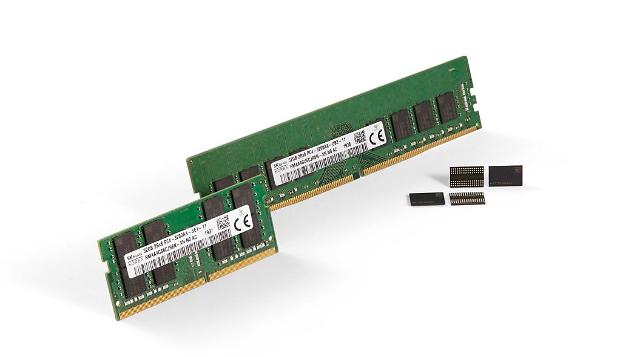

SK하이닉스는 3세대 10나노급(1z) 미세공정을 적용한 16기가비트(Gbit) DDR4 D램을 개발했다고 21일 밝혔다. [사진=SK하이닉스 제공]

©'5개국어 글로벌 경제신문' 아주경제. 무단전재·재배포 금지

![[포토] 윤석열 대통령, 4·19혁명기념탑 분향](https://image.ajunews.com/content/image/2024/04/19/20240419134308633606_388_136.jpg)

![[슬라이드 포토] 넷플릭스 시리즈 종말의 바보 제작발표회](https://image.ajunews.com/content/image/2024/04/19/20240419134605530571_388_136.jpg)

![[포토] 눈길 끄는 눈물의 여왕 김수현 벤츠](https://image.ajunews.com/content/image/2024/04/18/20240418134936718565_388_136.jpg)

![[포토] 제60회 한국보도사진전 개막](https://image.ajunews.com/content/image/2024/04/18/20240418134920458248_388_136.jpg)

![[금투세 폐지 논란] 코리아 디스카운트 심화...韓증시 불확실성 높여](https://image.ajunews.com/content/image/2024/01/03/20240103150426112900_388_136.jpg)